|                                                                                                                                                                                                        | Aims and Objectives                                                                                                                                                                                                                                                                                                                                                             |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| E 3.05<br>Digital System Design                                                                                                                                                                        | <ul> <li>How to go about designing complex, <i>high speed</i> digital systems (not just circuits)?</li> <li>How to use some of the modern <i>CAD tools</i> to help with the design?</li> <li>How to implement such designs using <i>programmable logic</i></li> </ul>                                                                                                           |  |  |

| Peter Cheung<br>Department of Electrical & Electronic Engineering<br>Imperial College London                                                                                                           | <ul> <li>How to implement such designs using <i>programmable logic</i> (e.g. FPGAs)?</li> <li>How to read <i>data sheets</i> and make sense of them?</li> <li>How do <i>digital building blocks</i> (such as memory chips, processing elements, arithmetic circuits etc.) work?</li> <li>How to interface to processors and computers (from hardware point of view)?</li> </ul> |  |  |

| URL: www.ee.ic.ac.uk/pcheung/<br>E-mail: p.cheung@ic.ac.uk                                                                                                                                             | <ul> <li>How to deal with testing of complex systems?</li> <li>Have fun!</li> </ul>                                                                                                                                                                                                                                                                                             |  |  |

| PYKC 3-Jan-08 E3.05 Digital System Design Topic 1 Slide 1                                                                                                                                              | PYKC 3-Jan-08 E3.05 Digital System Design Topic 1 Slide 2                                                                                                                                                                                                                                                                                                                       |  |  |

| Course Syllabus                                                                                                                                                                                        | Course Syllabus (1) – Programmable Logic                                                                                                                                                                                                                                                                                                                                        |  |  |

| <ul> <li>The course syllabus is divided into five main sections:</li> <li>Programmable Logic</li> <li>Arithmetic Circuits</li> <li>Data Encoding &amp; communication</li> <li>Architectures</li> </ul> | <ul> <li>Technologies behind programmable logic</li> <li>Programmable Logic architectures in general</li> <li>Complex Programmable Logic Devices (CPLDs)</li> <li>Field Programmable Gate Arrays (FPGAs)</li> </ul>                                                                                                                                                             |  |  |

Testing

- ◆ Recent advances in FPGAs

- Designing with FPGAs

- Design Flow, Design Tools, Design Libraries

- Future of programmable logic

Topic 1 Slide 3

| Course Syllabus (2) – Arithmetic Circuits                                                                                                                       | Course Syllabus (3) – Data Encoding &<br>Communication                                                                                                                                                                                           |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| <ul> <li>Adders architectures</li> <li>Multipliers circuits</li> <li>Floating point arithmetic circuits</li> <li>Other computational building blocks</li> </ul> | <ul> <li>Logic interface standards</li> <li>Clocking for high speed digital design</li> <li>Metastability issues</li> <li>Clock synchronisation</li> <li>Data encode and error correction</li> <li>On-chip and On-board communication</li> </ul> |  |  |

| <sup>r</sup> KC 3-Jan-08 Topic 1 Silde 5<br><b>Course Syllabus (4) – Hardware</b><br><b>Architectures</b>                                                       | PYKC 3-Jan-08 E3.05 Digital System Design Topic 1 Slide 6 Course Syllabus (5) – Digital Test                                                                                                                                                     |  |  |

| <ul> <li>Parallel vs serial</li> <li>Systolic and other array architectures</li> <li>Distributed arithmetic</li> <li>Cordic based architecture</li> </ul>       | <ul> <li>Modern packaging</li> <li>Board testing issues</li> <li>JTAG Boundary Scan</li> </ul>                                                                                                                                                   |  |  |

| YKC 3-Jan-08 E3.05 Digital System Design Topic 1 Slide 7                                                                                                        | PYKC 3-Jan-08 E3.05 Digital System Design Topic 1 Silde 8                                                                                                                                                                                        |  |  |

## **Recommended Books**

### Coursework

No perfect textbook for this course. Here are four reasonable possibilities:

- "Digital Design Principles and Practices", 4th Edition (Sept 2005), John F. Wakerly, Prentice Hall.

- This is a new edition of a well established textbook. It covers a significant portion of the materials taught on this course. At ~£45, this a bargain. Recommended purchase if you have not already done so!

- "Contemporary Logic Design", Gaetano Boriello, Randy H. Katz, August 2004, Prentice Hall.

- Good coverage on finite state machines and computer architectures. (~£45)

- "High-Speed Digital Design A handbook of black magic", Howard G. Johnson, Prentice Hall, 1993; ISBN 0-13-395724-1 (£61).

- The best practical guide to designing and building very high speed digital circuits. Expensive reference for your company to buy (not you).

- "FPGA-based System Design", Wayne Wolf, Prentice Hall, 2004, ISBN 0131424610 (£75)

- Contemporary book based on FPGA; possibly too expensive for what it covers

E3.05 Digital System Design

Topic 1 Slide 9

- Best way to learn DSD is to do it!

- Unassessed coursework:

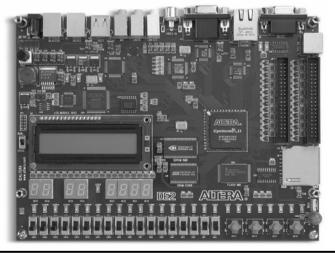

- 2 to 8 lab exercises using DE2 Board (from Altera) to learn the system

- Assessed coursework:

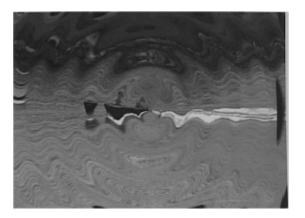

- Design of a cordic based processor to add ripple effect on an image

- Work in pairs one deliverable between the pair

- Deliverables:

- Working design and demonstrator

- Design document (effectively a no-nonsense report)

- Deadline: 1<sup>st</sup> day of the Summer Term

- Quartus-II software has a web-edition that can be downloaded (free) from Altera website after you register

- Software also available on all Level 5 & Level 1 machines

- DE2 Boards available on Level 5 and Level 1 Labs

PYKC 3-Jan-08

E3.05 Digital System Design

Topic 1 Slide 10

# Coursework – DE2 Board

http://www.altera.com/education/univ/materials/boards/unv-de2-board.html

# Coursework – Demo

This shows an example of the ripple video effect which is the goal of this coursework

E3.05 Digital System Design

Topic 1 Slide 11

## Levels of Design Abstractions

| Design<br>Levels | Design Descriptions | Primitive<br>Components | Theoretical Techniques   |

|------------------|---------------------|-------------------------|--------------------------|

| Algorithmic      | Specifications      | Functional blocks       | Signal processing theory |

|                  | High-level lang.    | 'black boxes'           | Control theory           |

|                  | Math. equations     |                         | Sorting algorithm        |

| Functional       | VHDL, Verilog       | Registers               | Automata theory          |

|                  | FSM language        | Counters                | Timing analysis          |

|                  | C/Pascal            | ALU                     |                          |

| Logic            | Boolean equations   | Logic gates             | Boolean algebra          |

|                  | Truth tables        | Flip-flops              | K-map                    |

|                  | Timing diagrams     |                         | Boolean minimization     |

| Circuit          | Circuit equations   | Transistors             | Linear/non-linear eq.    |

|                  | Transistor netlist  | Passive comp.           | Fourier analysis         |

## Topic 1

# Design Methodologies & Implementation Technologies

Peter Cheung Department of Electrical & Electronic Engineering Imperial College London

> URL: www.ee.imperial.ac.uk/pcheung/ E-mail: p.cheung@imperial.ac.uk

| PYKC | 3-Jan-08 |

|------|----------|

|      |          |

E3.05 Digital System Design

Topic 1 Slide 13

# The Design Process

# The Design Process (cont')

#### Top-down design strategies

- Refine Specification successively

- Decompose each component into small components

- Lowest-level primitive components

- Over-sold methodology only works with plenty of experience

#### Bottom-up design strategies

- Build-up from primitive components

- Combined to form more complex components

- Risk wrong interpretation of specifications

#### Mixed strategies

- Mostly top-down, but also bits of bottom-up

- Reality: need to know both top level and bottom level constraints

| Ρ | Y٢ | C | 3 | Jar | 1-O | 8 |

|---|----|---|---|-----|-----|---|

| Ρ | Y٢ | C | 3 | Jar | 1-O | 8 |

# **Design Descriptions**

## **Design Tools**

| Schematic capture                                                                                                                                                                                                      | Hardware Description<br>Languages                                                                                                                                                                                    | Modern_dia                                                             | ital design systems contain the mo                                                            | ost of the followin                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Good for multiple data flow<br>Give overview picture<br>Relates to hardware better<br>Doesn't need to be good in computing<br>High information density<br>Back annotations possible<br>Mixed analogue/digital possible | Flexible & parameterisable<br>Excellent for optimisation & synthesi<br>Direct mapping to algorithms<br>Excellent for datapaths<br>Readily interfaced to optimiser<br>Easy to handle and transmit<br>(electronically) | features:<br>• Schematio<br>• Hardwar I<br>• Logic Synt<br>• Timing An | Capture • Symbol Ed<br>Description Language • Simulation<br>thesis & Optimisation • Autoplace | diting<br>n with Timing<br>ment and Routing<br>Editing |

| Not good for algorithms<br>Not good for datapaths<br>Doesn't interface well in optimiser<br>No good for synthesis software<br>Difficult to reuse<br>Not parameterisable                                                | Essentially serial representation<br>May not show overall picture<br>Often need good programming skill<br>Divorce from physical hardware<br>Need special software                                                    | • Hierarchic                                                           | al Design Management                                                                          |                                                        |

| Jan-08 E3.05 [                                                                                                                                                                                                         | igital System Design                                                                                                                                                                                                 | Topic 1 Slide 17 PYKC 3-Jan-08                                         | E3.05 Digital System Design                                                                   | Topic 1 S                                              |

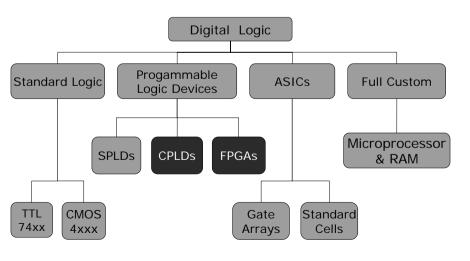

| A typical dig                                                                                                                                                                                                          | ital system                                                                                                                                                                                                          |                                                                        | mplementation Technol                                                                         | ogies                                                  |

| A typical dig                                                                                                                                                                                                          | ital system                                                                                                                                                                                                          |                                                                        | mplementation Technol                                                                         | ogies                                                  |

|                                                                                                                                                                                                                        | ital system<br>M/ROM Buffer memo                                                                                                                                                                                     |                                                                        | Digital Logic                                                                                 | Full Custom                                            |

| Microprocessor RA                                                                                                                                                                                                      |                                                                                                                                                                                                                      | ries<br>Standard Lo                                                    | Digital Logic                                                                                 | Full Custom<br>Microprocessor<br>& RAM                 |

# ologies